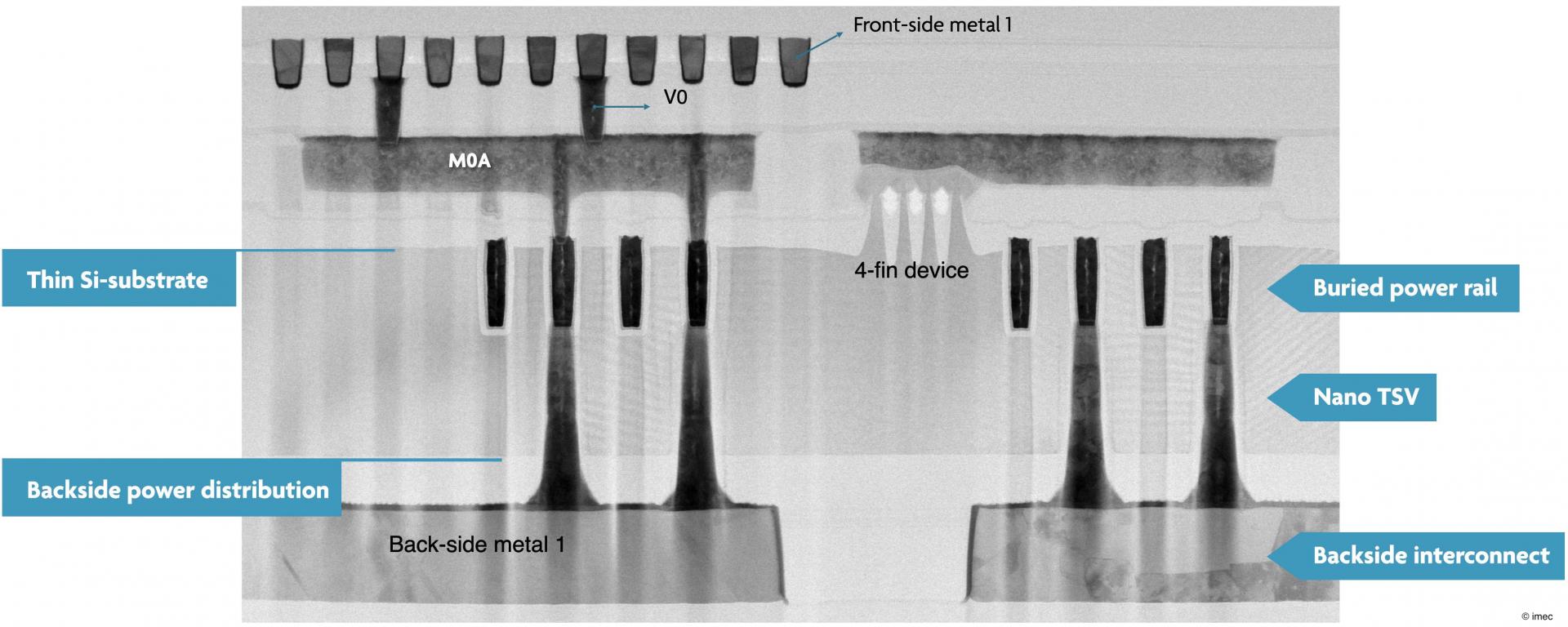

The conventional metal layers on the frontside of the wafer will be used for routing signals, while the metal layers at the back of the wafer will be used for power delivery.

Separating the power delivery and signal routing enables lower voltage drop in the power supply (which improves performance) and reduces congestion of metal routing on the frontside.

Intel has announced that they will introduce this at the 2nm node with nanosheet devices.

TEM image showing scaled FinFETs connected to the wafer’s backside and frontside.

The device architecture beyond nanosheets and forksheets is complementary FETs (CFETs) where N and P devices are stacked on top of each other using a complex integration. There are several flavours of CFETs possible, and we are in the early stages of pathfinding.

There are several flavours of CFETs possible, and we are in the early stages of pathfinding.

In the back-end metallization, copper dual-damascene integration will give way to high aspect ratio metal etch to pattern lines below 20nm pitch.

We have been focusing on enabling Ruthenium for direct metal etch. To lower the resistance, the aspect ratio of Ruthenium will be increased along with airgaps to reduce the capacitance impact.

These changes will ensure that the back-end RC(resistance-capacitance) scaling roadmap continues for several nodes.