Both Calibre tools are certified by GF, so mutual customers designing for the new GF Fotonix platform can continue to use the trusted Calibre nmPlatform for silicon photonic devices as they have used for previous offerings.

“While silicon photonic designs and their subsequent inclusion into multi-die offerings introduce new verification complexities, these complexities are addressed in the Calibre silicon photonics design kits, which require no change to how designers traditionally use Calibre,” says Siemens’ Michael Buehler-Garcia.

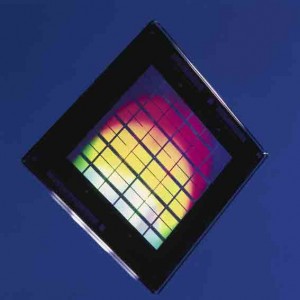

Silicon photonic devices contain curved layouts, rather than the linear Manhattan grid features found in traditional CMOS designs.

Applying traditional CMOS DRC to silicon photonic layouts yields numerous false positive errors that design teams must often spend weeks tracking down.

To address this challenge, GloFo leverages Siemens’ Calibre eqDRC software, which allows rule checks to use equations in place of, or in addition to, linear measurements.

This helps enable more accurate results, leading to significantly fewer errors, so design teams can spend far less time and fewer resources debugging their designs.

Similarly, the curvilinear nature of photonic structures, together with the general lack of source netlists for optics, poses a challenge when performing LVS checking.

Traditional IC LVS technology extracts physical measurements from well-understood electronic structures and compares them to the intended corresponding elements in the source netlist.

However, with curved structures it is difficult, if not impossible, to discern where one structure begins and another ends.

With the new GloFo Fotonix PDK with Calibre LVS, this obstacle is resolved with the use of text and marker layers to discern regions of interest.

Silicon photonic devices are often implemented in an individual die on a specific process node, then stacked and packaged with the rest of design components in multiple dies using advanced heterogeneous packaging technologies.