Among the key targets in place-and-route—performance, power, and area (PPA) — performance has traditionally been the primary focus. Low power has been gaining in importance though, particularly at today’s advanced process nodes. Of course, no one wants lower-performing chips, so place-and-route tools employ a variety of strategies to achieve the lowest power without sacrificing performance.

Place-and-route software is not all the same. Older software architectures on the market use multiple different data models, which means lots of inefficient communication between all the engines involved (placement, routing, clock-tree-synthesis). Designers shouldn’t suffer delays in time-to-closure and sub-optimal results because their place-and-route tool is clumsy. A design tool built on a single-unified data model and using modern algorithms is faster, easier to use, and capable of producing the best PPA for today’s hierarchical and block-level designs. Sporting a very capable software architecture is just the foundation for achieving low power during place-and-route. The tool must also:

- Handle multiple power domains deftly

- Perform advanced PowerFirst optimizations throughout the flow

Managing multiple power domains

Multi-power domain support ensures all the elements required in a low power design are included and used in accordance with the low-power specs. The software used in the digital implementation flow must be able to buffer on multiple power domains without errors and perform placement of all power management cells such as level shifters, isolation cells, power switch cells, and retention flip-flops. Power-sensitive designs also require routing secondary power/ground pins and routing to the power grid inside the voltage islands.

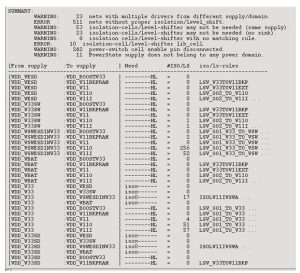

Look for place-and-route software that offers comprehensive multi-power domain support and supports the Unified Power Format (UPF). It is very useful to have a built-in Power Domain Checker (Figure 1) to flag any errors related to power domain, cell placement, connectivity, and buffering without the need of an external tool.

Figure 1. Built-in Power Domain Checker.

PowerFirst methodology for no-compromise low power

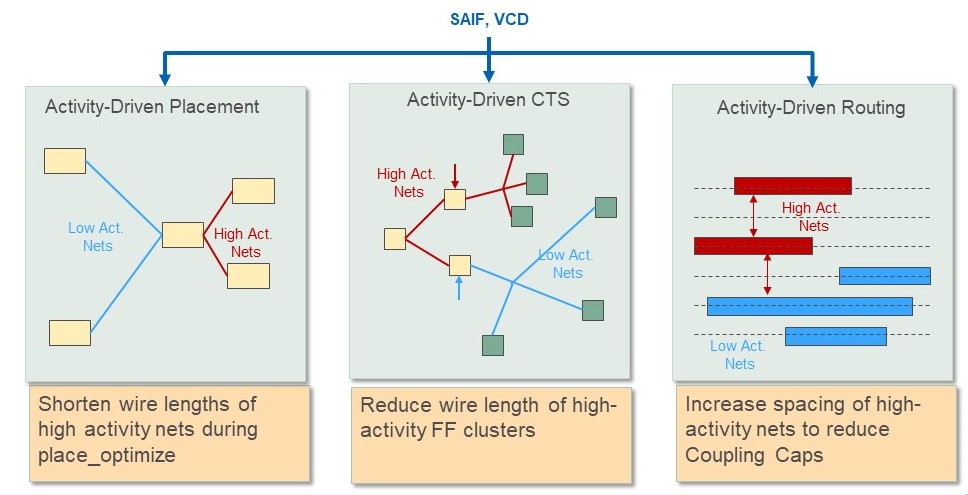

To meet strict power specifications without sacrificing performance, the place-and-route tool should use low power as the top priority and work towards that goal throughout the flow, using techniques like activity-driven placement and routing for lower dynamic power. Figure 1 shows how the placement engine will use switching information reduce the capacitance on high-activity nets. It does throughout the flow, including during clock tree synthesis by keeping high-activity net connections short, while spreading out the low-activity nets to relieve congestion. The router spaces high-activity nets to reduce coupling capacitance and reduce power, but can use switching information to make decisions about what rules to apply to high- and low-activity nets.

Figure 2. Managing coupling capacitance at various steps with activity-driven optimizations.

With this PowerFirst methodology, the place-and-route flow can achieve the best possible power for that node, library, and design specs, and then optimize from that point to reach the timing target. This method is more effective than trying to recover power once the most power-hungry cells have already been used in the design to achieve timing.

Techniques deployed in a PowerFirst methodology include:

- Clock transition fixing for better power – slowing down the sharp transition of the buffers on the clock tree without causing transition violations.

- Tradeoff small timing for large power reduction in CTS – balancing skew intelligently.

- Multi-bit-register merging and de-merging – merging low-bit flip-flops into higher-bit flip-flops.

- Full LVF analysis and optimization – managing the effects of on-chip variation.

Example Results from a Commercial Place-and-Route Tool’s PowerFirst Methodology

The Siemens’ Aprisa place-and-route software uses PowerFirst optimization to reduce the internal, switching, and leakage power of the most power-sensitive designs while minimizing timing tradeoffs. In an industrial 7 nm design, a DDR PHY with about 1.3M instances and a 1 GHz frequency, PowerFirst techniques reduced the total power by 16% compared to Aprisa in timing-only mode while maintaining the achieved timing correlated to signoff. Aprisa’s results also beat the incumbent place-and-route solution.

It’s possible to achieve lower power usage during place-and-route by using software designed to do so with the following features:

- Full support for all industry-standard power formats and for multiple power domains, including offering a built-in power domain checker.

- A unified data model that is shared throughout the entire flow that allows real routing information and parasitics to be available to each step in the flow, resulting in consistent timing and DRC and excellent correlation to signoff tools.

Learn more about the low-power place-and-route software from Siemens in our new technical paper. https://resources.sw.siemens.com/en-US/white-paper-aprisa-place-and-route-for-low-power-socs

Author: Janet Attar